現(xiàn)貨庫存,2小時(shí)發(fā)貨,提供寄樣和解決方案

熱搜關(guān)鍵詞:

氮化鎵(GaN)功率器件憑借低寄生電容、高開關(guān)速度與優(yōu)異熱性能,正廣泛應(yīng)用于高頻DC-DC轉(zhuǎn)換器、數(shù)據(jù)中心電源與D類放大器等高效率系統(tǒng)中。然而,其對PCB布局極為敏感,尤其在高di/dt和dv/dt條件下,寄生參數(shù)易引發(fā)振鈴、EMI問題甚至器件損壞。ADI推出的100V半橋GaN驅(qū)動器LT8418集成了分離式柵極驅(qū)動、智能自舉開關(guān)與高驅(qū)動能力,專為應(yīng)對高速GaN應(yīng)用挑戰(zhàn)而設(shè)計(jì)。要充分發(fā)揮其性能,必須遵循嚴(yán)格的PCB設(shè)計(jì)規(guī)范。

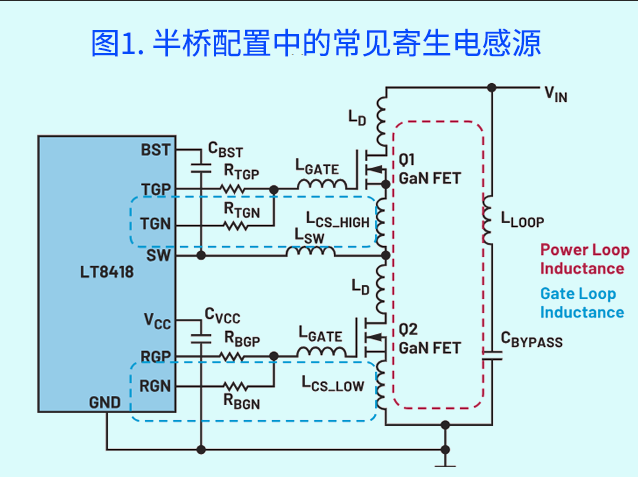

1. 最小化寄生電感是關(guān)鍵

GaN轉(zhuǎn)換器的振鈴主要源于功率環(huán)路與柵極環(huán)路中的寄生電感。功率環(huán)路電感(包括FET漏極電感LD、共源電感LCS及走線電感)會導(dǎo)致開關(guān)節(jié)點(diǎn)電壓過沖,增加開關(guān)損耗與EMI。柵極環(huán)路電感則引發(fā)柵極信號振鈴,可能造成誤導(dǎo)通或超過±6V柵極絕對最大額定值,導(dǎo)致永久性損傷。因此,降低兩類環(huán)路電感是設(shè)計(jì)核心。

2. 采用內(nèi)部垂直布局優(yōu)化熱回路

為最小化熱回路電感,推薦使用內(nèi)部垂直布局:將高側(cè)與低側(cè)GaN FET并排放置在同一PCB層,高頻去耦電容(低ESR陶瓷電容)緊鄰FET源極與漏極布置。利用內(nèi)層作為返回路徑,使其與頂層走線緊密耦合,形成小面積電流環(huán),顯著降低雜散電感。該結(jié)構(gòu)使熱回路電感與板厚無關(guān),且正反向電流磁場相互抵消,進(jìn)一步抑制電感效應(yīng)。

3. 熱回路電容布局優(yōu)化散熱

在降壓拓?fù)渲校邆?cè)FET通常承受更高熱應(yīng)力。建議將熱回路電容靠近低側(cè)FET放置,為高側(cè)FET留出更多銅箔空間用于散熱。VIN平面布置于FET下方內(nèi)層。升壓拓?fù)鋭t相反,電容應(yīng)靠近高側(cè)FET,為低側(cè)FET散熱留出空間,返回地平面置于第二層。

4. 善用通孔降低電感與熱阻

在GaN FET焊盤上布置多個(gè)填充通孔,可有效降低寄生電感與熱阻。由于漏極與源極交錯(cuò),通孔中反向電流產(chǎn)生的磁場相互抵消,減少整體電感。同時(shí),通孔將熱量傳導(dǎo)至多層PCB的銅平面,提升散熱能力。填充通孔可防止焊接時(shí)氣孔與焊料泄漏,增強(qiáng)可靠性。

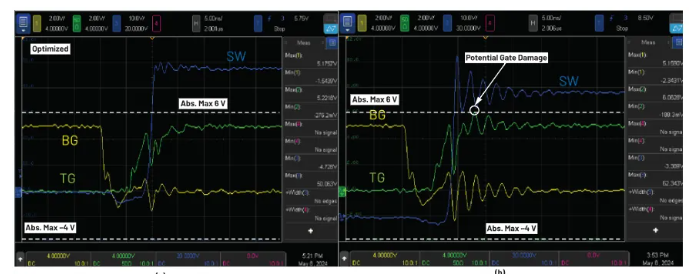

5. 精細(xì)調(diào)節(jié)柵極電阻控制dv/dt

LT8418支持分離式柵極驅(qū)動,允許通過外接RG_ON與RG_OFF獨(dú)立調(diào)節(jié)導(dǎo)通與關(guān)斷擺率。合理選擇柵極電阻可抑制振鈴、優(yōu)化EMI并防止直通。建議從較高阻值(如3.3Ω)開始測試,在最大負(fù)載與最高輸入電壓下監(jiān)測柵極波形,逐步減小電阻直至效率與信號完整性達(dá)到平衡。圖2示顯示,1Ω電阻導(dǎo)致柵極過沖超限,而2Ω可實(shí)現(xiàn)干凈波形。

圖2示顯示,1Ω電阻導(dǎo)致柵極過沖超限,而2Ω可實(shí)現(xiàn)干凈波形。

6. 正確測試點(diǎn)布局避免誤判

使用短開爾文連接測量柵極信號,避免長引線引入寄生電感。測量底部柵極時(shí),探頭接地彈簧應(yīng)靠近FET GND。頂部柵極信號以開關(guān)節(jié)點(diǎn)為參考,需使用高速差分探頭,并推薦MMCX連接器以減少干擾。不當(dāng)測試點(diǎn)會導(dǎo)致虛假振鈴,誤導(dǎo)設(shè)計(jì)判斷。

深圳市中芯巨能電子有限公司代理銷售ADI(亞德諾)旗下全系列IC電子元器件,為制造業(yè)廠家的工程師或采購提供選型指導(dǎo)+數(shù)據(jù)手冊+樣片測試等服務(wù)。如需LT8418產(chǎn)品規(guī)格書、樣片測試、采購等需求,請加客服微信:13310830171。